KAIST, 레이저 이용으로 반도체칩 발열 최소화해 성능 향상

[파이낸셜뉴스] 한국과학기술원(KAIST) 기계공학과 김정원 교수팀이 레이저를 이용해 반도체 칩 내에서 초저잡음 클럭(clock) 신호를 1천조 분의 1까지 정확하게 생성하고 분배할 수 있는 기술을 개발했다. 이 기술로 클럭 분산과정에서 발생하는 칩 내에서의 발열을 기존 1.2도에서 0.1도로 낮췄다.

기존에는 클럭 신호의 정확성이 통상적으로 1조 분의 1초(피코초) 수준이었으나, 이를 1천배 빠르게 해 3차원 적층칩을 비롯한 반도체 칩의 성능을 향상시킬 수 있다.

김정원 교수는 9일 "현재 아날로그-디지털 변환기와 같은 고속 회로에 매우 낮은 지터의 샘플링 클럭 신호를 공급해 성능을 향상하는 연구를 진행 중"이라며 "3차원 적층 칩과 같은 구조에서 발열을 줄일 수 있을 지에 대한 후속 연구도 계획 중"이라고 말했다.

최근 반도체 칩의 성능이 급격하게 향상돼 보다 정확한 타이밍으로 칩 내의 다양한 회로 블록들의 동작을 동기화시키는 클럭 신호를 공급하는 기술이 중요하다.

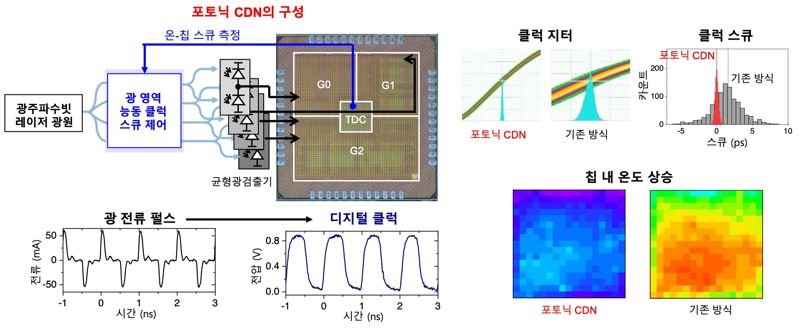

고성능의 반도체 칩 내에서 클럭 신호를 분배하기 위해서는 클럭 분배 네트워크(CDN)에 많은 수의 클럭 드라이버들을 사용해야 한다. 이로 인해 발열과 전력 소모가 커질 뿐 아니라 클럭 타이밍도 나빠지게 된다. 칩 내의 클럭 타이밍은 무작위적으로 빠르게 변화하는 '지터'와 칩 내의 서로 다른 지점 간의 클럭 도달 시간 차이에 해당하는 '스큐'에 의하여 결정되는데, 클럭 드라이버들의 개수가 늘어남에 따라 지터와 스큐 모두 통상 수 피코초 이상으로 커지게 된다.

연구진은 이를 해결하기 위해 펨토초 이하의 지터를 가지는 광주파수빗 레이저를 마스터 클럭으로 하는 새로운 방식의 클럭 분배 네트워크 기술을 개발했다. 이는 광주파수빗 레이저에서 발생하는 광 펄스들을 고속 광다이오드를 이용해 광전류 펄스로 바꾼 뒤 반도체 칩 내의 금속 구조 형태로 된 클럭 분배 네트워크를 충전 및 방전하는 과정을 통해 구형파 형태의 클럭 신호를 생성하는 방식이다.

특히 이 기술로 클럭 분배 네트워크의 클럭 드라이버들을 제거한 금속 구조만을 통해 칩 내에서 클럭을 분배할 수 있어, 타이밍 성능을 개선할 수 있을 뿐만아니라 칩 내 발열도 획기적으로 줄였다. 그 결과 지터와 스큐를 기존 대비 100분의 1 수준인 20펨토초 이하로 낮춘 뛰어난 타이밍 성능을 보였다. 또한 칩내 클럭 분산 과정에서의 전력소모 및 발열 역시 기존 방식 대비 100분의 1 수준으로 낮췄다.

monarch@fnnews.com 김만기 기자

※ 저작권자 ⓒ 파이낸셜뉴스, 무단전재-재배포 금지